[第 6 部:技術詳細編]

関所の罠 ―― なぜBig Techは真の『物理的AI国家』になれないのか

序:Big Techが抱える「究極の死角」

「日本が光コンピュータで 100 YottaFLOPS を実現するなら、資金力のある Google や Microsoft ならもっと強力な光TPU群を作れるのではないか?」という疑問があるだろう。

結論から言えば、彼らもすでにデータセンター内部では「光(3進数に近い多値演算)」を実用化しつつある。我々と同じアプローチだ。しかし、彼らには 「絶対に超えられない物理得・商業構造的ボトルネック」 が存在する。

それが 「関所」 の存在である。

構造的ボトルネック:『関所』の可視化

Big Tech がグローバル市場(2進数世界)を相手にする以上、避けて通れない「変換の壁」を構造化する。

graph TD

subgraph "Big Tech (グローバル・プロトコル)"

GTOR["光TPU (内部演算)"] -->|位相/3進数| GGW["OSCL 関所"]

GGW -->|変換熱 / 遅延| GETH["2進数イーサネット"]

GETH -->|TCP/IP| GUser["外部ユーザー/デバイス"]

end

subgraph "AI国家 (ネイティブ・プロトコル)"

JTOR["Grand-Master v10"] -->|純粋位相| JGrid["全光ネットワーク"]

JGrid -->|変換ゼロ| JEdge["3進数エッジ/ロボット"]

end

style GGW fill:#991b1b,stroke:#b91c1c

style JEdge fill:#0369a1,stroke:#0284c7変換の壁:『関所』で発生する致命的ロス

Google の巨大データセンターの中で、どれほど光TPUが超光速・極低温で「3進数(多値)」の高度な推論を行ったとしても、彼らが商売をする相手は「アメリカの一般消費者」「世界中のスマートフォン」「数億台のIoT家電」である。

そして、その外の世界(インターネットと物理デバイス)はすべて 「2進数の電気信号(TCP/IP、IPv4/v6、シリコンチップ)」 で構築されている。

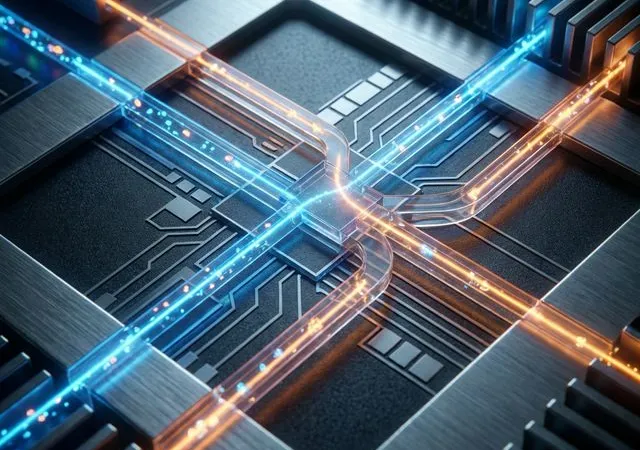

- 次元の不一致(翻訳ロス) : 光TPUが計算した「-1, 0, 1(位相)」の結果を、世界中のスマホへ送信(映像出力や音声応答)するためには、データセンターの出口にある巨大な Gateway(変換基板) を通り、電気の長短「0, 1」へと翻訳・圧縮し直さなければならない。

- 熱と遅延の非対称性 : この「光信号 → 電気信号」への再変換には、マッハツェンダー干渉計や極低温バッファといった「光電融合インターフェース」が必要となる。この関所を毎秒何十億回と通過するたびに、 莫大な変換ロス、パケット再組立てによる遅延(レイテンシ)、そして強烈な『熱』 が発生する。

彼らは「グローバル市場のすべてのデバイスを光3進数に買い替えさせる」ことなど不可能だ。したがって、未来永劫、この「2進数(電気)の関所」を維持し、そこに莫大な電力を注ぎ込み続けなければならない。

日本の解答:「ネイティブ3進数」によるゼロ・レイテンシ

一方、日本の「国家改造計画」はアプローチが根本から異なる。 日本の5カ所にあるTPUセンターは、計算結果をわざわざ「2進数(インターネットプロトコル)」へ変換しない。

なぜなら、日本は100兆円を投じて 「列島中のインフラデバイス(信号機、自動運転車、工場ライン、家庭用 ホーム 8 エッジチップ)」そのものを、すべてネイティブな3進数・光通信対応へダウンサイジング・換装 するからだ。

-

関所の撤廃 : センターの光チップで生まれた「光の波(思考)」は、変換(翻訳)されることなく、IOWN(オール光ネットワーク)をそのまま通過し、エッジ側の「光」対応アクチュエータ(モーターやセンサー)を直接駆動させる。

-

物理層の直結 : これにより、変換時の熱ロスも遅延もゼロになる。日本のセンターは、1億インフラデバイスと 「まるで同一の基板上(マザーボード内)」に存在するかのように 直接物理挙動を支配できる。

結論:鎖国がもたらす物理的優位

Google が「グローバルな旧規格(2進数インターネット)」に縛られ、関所で渋滞を起こしている間に、日本は国内(ガラパゴス)という物理的閉鎖空間を逆手にとり、 「センサーからセンターまで100%光・3進数で一貫した、真のゼロ・レイテンシ・アーキテクチャ」 を完成させる。

Big Tech は「優秀なクラウドAI」であっても、この関所がある限り「物理現実をミリ秒単位で制御する国家OS」には決してなれないのである。

TECH-SPEC: The Gateway Bottleneck

- Big Tech アーキテクチャ: [光TPU (内部演算)] ➜ [OSCL 関所 (熱/遅延)] ➜ [TCP/IP (2進数エッジ)] 結果: 莫大な電力浪費と通信レイテンシの発生。

- AI国家ネイティブ・アーキテクチャ: [Grand-Master v10 (光)] ➜ [IOWN光グリッド (変換ゼロ)] ➜ [3進数エッジ (ホーム 8/Drive-Sense)] 結果: 変換ロス・ゼロによる「物理制御の完全掌握」。

[!NOTE] 専門用語の詳細は AI国家コンセプト用語集 をご参照ください。