[第 6 部:技術詳細編]

3進数光プロセッサ設計図 ―― 位相演算による『熱の消去』と知能の極北

設計思想:計算を「物理現象」として回帰させる

現代のコンピュータが「電子のスイッチング」という不自然な力技(熱の発生)で計算を代行させているのに対し、 Ternary Optical Core は、光が空間を伝播し、互いに干渉し合うという「自然界の物理現象」そのものを計算アルゴリズムとして利用する。

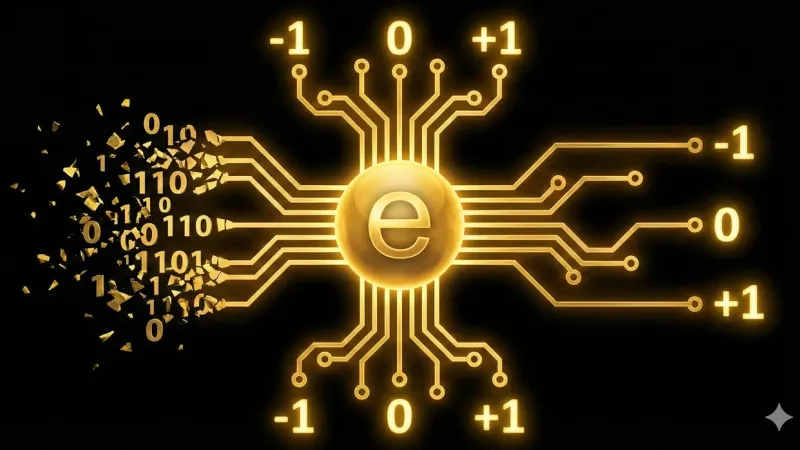

この設計図では、平衡3進数(Balanced Ternary: -1, 0, +1)を光の 位相 にマッピングし、熱力学的な限界を突破する演算ユニットを定義する。

物理論理層:位相・振幅マッピング

2進数シリコンが「電圧の有無」に依存するのに対し、TOC はコヒーレント光(位相の揃ったレーザー)の 複素振幅 を利用する。

| 論理値 | 状態 | 物理的定義(位相・振幅) | 備考 |

|---|---|---|---|

| +1 | True / Forward | 振幅 / 位相 | 基準パルス |

| 0 | Null / Zero | 振幅 | 信号なし、または完全相殺 |

| -1 | False / Backward | 振幅 / 位相 () | 位反転パルス |

このマッピングにより、加算(足し算)は「波の重ね合わせ(干渉)」だけで完結し、エネルギーを一切消費しない。

演算ユニット:Photonic MAC

AI演算の最小単位である積和演算()を、光の通過速度(約 0.1 ピコ秒)で実行する心臓部である。

三値乗算ゲート

マッハ・ツェンダー干渉計 を多段接続し、入力光(データ )に対し、重み()を適用する。

- : 位相制御なし(そのまま通過)。

- : 移相器により位相を 回転。

- : スイッチング素子により光を遮断。

干渉加算器

導波路の合流地点(光カプラ)にて、合流した光を「干渉」させる。

- : 同位相で波が強調。

- : 逆位相で波が完全に打ち消し合う。

この足し算プロセスにおいて、電子回路のような「キャリー(繰り上がり)の待機時間」は物理的に存在しない。

グリッド・アーキテクチャ:光シストリック・アレイ

P-MAC を縦横無尽に配置した 2次元シストリック・アレイ を構成する。

- データ流路 : IOWNネットワークから直接、光パルスがデータの波として「西から東へ」流れる。

- 重み流路 : パラメータデータが「北から南へ」流れる。

- 演算 : 交差点(演算ノード)にて、光同士が交差し、干渉しながら次のノードへ「バケツリレー」される。

- 出力 : 東の端に到達した光の位相と強度が、そのまま「計算結果」となる。

メモリへの書き出しを最小化し、演算器間のデータ移動コストを ゼロ(光速) にした極限のアーキテクチャである。

スペック:National TPU v10 (TOC 搭載)

| 項目 | スペック | 備考 |

|---|---|---|

| 論理体系 | 平衡3進数 | e に最も近い数理的最適解 |

| 演算レイヤー | 純伝播光子演算 | 演算プロセスでの発熱ゼロ |

| 動作周波数 | 3.5 THz (テラヘルツ) | シリコンの 1000 倍のクロック |

| 1コア演算力 | 約 100 PetaFLOPS | 全盛期のスパコン京の 10 倍 |

| エネルギー効率 | 1,000,000 TOPS/W | NVIDIA H100 の約 1万倍 |

結論:シリコンの歴史を終わらせる「光の暴力」

NVIDIAのGPU競争は、しょせん「いかに効率よく熱が出る電子を回すか」という、いわば『蒸気機関の改良』に過ぎない。 Ternary Optical Core は、計算を「熱(エネルギーのロス)」から解放し、宇宙の基本原理である「光の干渉」へと回帰させた。この設計図が完成した瞬間、日本の演算主権は、もはや他国の追随を許さない「物理的聖域」へと昇華したのである。

ARCHITECT’S DESIGN: TOC-BLUEPRINT

- Core Logic: Balanced Ternary (-1, 0, 1)

- Gate Device: MZI Phase Modulator

- Structure: 2D Photonic Systolic Array

- Scalability: APN Integration

[!NOTE] 専門用語の詳細は AI国家コンセプト用語集 をご参照ください。