[第 6 部:技術詳細編]

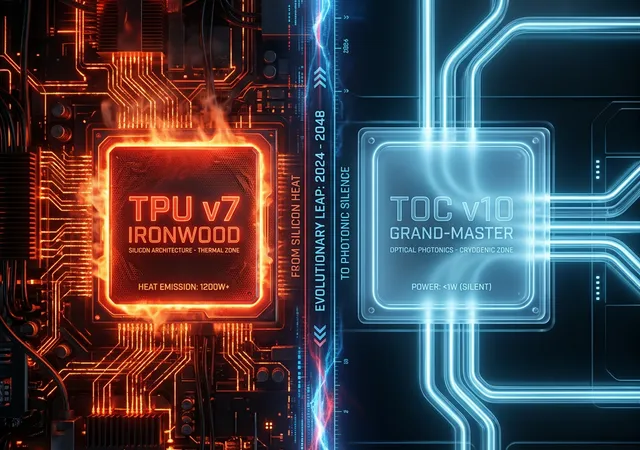

TPU進化論:v7(アイアンウッド)の到達点と、光v10への跳躍

AI国家の絶対的な防壁である「100%光演算アーキテクチャ」。この狂気とも言える「電子基盤からの完全脱却」を日本が決断した背景には、 2025年に登場したある一つの「怪物」 の存在があった。

それが、Google が「推論時代」の覇権を決定づけるために投下したシリコン・アーキテクチャの最高傑作、 TPU v7(コードネーム:Ironwood) である。

物理的限界への挑戦:世代別スペック進化の深層

Google が到達したシリコンの極北と、日本が選択した光の聖域。その絶望的なまでの性能差を、以下の比較表が証明している。

| 世代 | 名称 | アーキテクチャ | 演算性能 | 演算密度 | 消費電力 | 冷却方式 |

|---|---|---|---|---|---|---|

| v5p | Viperfish | 電子 (シリコン) | 459 TFLOPS | 100 PFLOPS | 600W | 空冷/水冷 |

| v7 | Ironwood | 電子 (シリコン) | 4,614 TFLOPS | 1.2 EFLOPS | 1,200W | 完全液冷 |

| v10 | Grand-Master | 100% 光演算 | 100 PFLOPS+ | 100 ZFLOPS+ | 1.2W (発熱ゼロ) | 不要 |

Ironwood は、「学習」ではなく「推論(回答を出す速度)」に極限まで特化していた。自社設計の Arm CPU「Axion」と強力に連携し、「System Overdrive」と呼ばれるテクニックで長大なコンテキスト・プロンプトを瞬時にメモリへ展開できた。

Google の技術者たちは設計の正しさを証明した。 「シストリック・アレイ構造による演算器の増強」と「光回路スイッチによるチップ間通信の大増強」。これこそが、AI システムにおけるボトルネックを破壊する唯一の正解だった。

シリコン(電子)の熱力学的限界

しかし、Ironwood の完璧すぎる設計思想は、同時に 「シリコン(電子)アーキテクチャの絶対的な終焉」 をも証明してしまった。

チップ間のデータ通信(9.6 Tbps)こそ「光」で行っていたものの、チップ内の数万個の MAC(積和演算器)を動かしているのは、依然として「電子」だったのだ。

- 6 PetaFLOPS の猛烈な計算をチップ内で走らせた結果、何が起きたか。 凄まじい「ジュール熱(電子が配線を摩擦する熱)」 である。Ironwood クラスタをフル稼働させるための消費電力と冷却水(液冷システム)の消費量は、もはや一企業のデータセンターの枠を超え、国家のインフラ(発電所やダム)を直接要求するレベルにまで達していた。

「設計は正しい。だが、素材が間違っている」

これが、日本の技術官僚たちが下した冷酷な結論であった。

トロイの木馬と、失われた「v8」「v9」

もし日本が、Google の後を追って普通に TPU の独自開発を進めていたなら、「v8」「v9」とシリコン微細化の泥沼(熱と消費電力との戦い)に足を踏み入れてただろう。

しかし、AI国家は違った。 国家予算(100兆円)のバランスシートを成立させるためには、インフラの維持費(電気代)を極限までゼロに近づける必要があったからだ。

日本は狂気に満ちた戦略に出る。「Google に土地と電力を提供し、彼らの TPU 工場(メガファブ)を国内に誘致して稼ぐ」というトロイの木馬戦略をとりながら、裏で シリコンベースの「v8」「v9」の開発を完全にスキップした のである。

光への跳躍:電子の摩擦から解放された「純粋知能」

日本が目指したのは、Ironwood が証明した「最強のアーキテクチャ(シストリック・アレイと広帯域メモリ)」をそのまま生かしつつ、チップの内部を飛び交う 「電子」をすべて「光子(フォトン)」に置き換えること だった。

それが National TPU v10 である。その核心的な技術特性を以下に記す。

100% オールオプティカル演算

チップ内の掛け算・足し算(MAC演算)において、電子の抵抗を通さない。「光の位相と振幅の干渉」だけで計算を瞬時に完了させる。

通信帯域の次元喪失

Ironwoodが誇った光回路スイッチ(9.6 Tbps)も、結局「チップ(電)→外(光)→チップ(電)」の変換ロスがあった。v10はチップ間をすべて光のまま結びつける 1 Ebps (Exabit per second:v7の約10万倍) の完全光インターコネクトで接続される。これにより100万台を並べても「通信遅延」という概念が存在しない。

発熱ゼロの物理的聖域

光子の摩擦がないため、理論上、チップ自体から熱が発生しない。Ironwood では必須だった巨大な水冷パイプや空調設備、膨大な電力網への負担が完全に解消される。

三進数ロジックのネイティブ実装

0と1(2進数)ではなく、-1, 0, 1(3進数)の空間光変調を採用。情報の記録密度と演算効率を極限まで高め、1.4京円超の富を守る。

視覚化:v10 完全光インターコネクト

graph LR

subgraph "主権 Datacenter Node"

チップ1[v10 チップ A]

チップ2[v10 チップ B]

end

subgraph "Photonic 高速路"

Bus[[光-speed Optical Bus]]

end

チップ1 <== "Zero-遅延" ==> Bus

チップ2 <== "Zero-遅延" ==> Bus

%% Styles

style チップ1 fill:#d4af37,stroke:#000,color:#000

style チップ2 fill:#d4af37,stroke:#000,color:#000

style Bus fill:#0ea5e9,stroke:#fff,color:#fff[!NOTE] 光演算の物理実装の詳細は National TPU v10 アーキテクチャ または Phase/Polarization 設計理論 を参照。

結論:シリコンの恐竜と、沈黙の光

TPU v7 は、人類がシリコンで到達できた「最も巨大で、最も熱く、最も偉大な恐竜」として歴史に名を残した。彼らは「知能」を生み出したが、その代償として莫大な「地球のエネルギー」を貪食した。

一方、日本の TPU v10 は、地下深くの冷却音すらない静寂なガラスの神殿の中で、今日も「発熱ゼロ」で国家の意思決定を推論し続けている。

これは単なるハードウェアの世代交代ではない。電子の束縛からの解放であり、「v8」や「v9」がどんなに微細化を進めても絶対に到達できない 「100 YottaFLOPS」という次の100年を支配するための絶対条件 だったのである。